Während sie die einen – Entwickler und Leiterplattendesigner – lieben, weil der Platz für die Entflechtung von Leiterplatten aufgrund der immer kleineren Bauteile bei immer höheren elektrischen Anforderungen immer geringer wird, sind sie für die anderen – die Baugruppenhersteller – wegen der Risiken bei der Baugruppenfertigung oft ein großes Problem.

Die Rede ist von Durchkontaktierungen in Anschlußflächen oder Vias in Pads.

Nun gab es für Leiterplattendesigner lange Zeit die klare Regel, daß Durchkontaktierungen in Anschlußflächen von SMD-Bauteilen unzulässig sind und zunächst über ein fan-out mit einer kurzen Leiterbahn von diesen entfernt werden müssen. Diese Regel wird inzwischen teilweise aus Unkenntnis über die Folgen, teilweise durch eine höhere Risikobereitschaft zunehmend in Frage gestellt und es werden zunehmend Durchkontaktierungen direkt in die Anschlußflächen gesetzt.

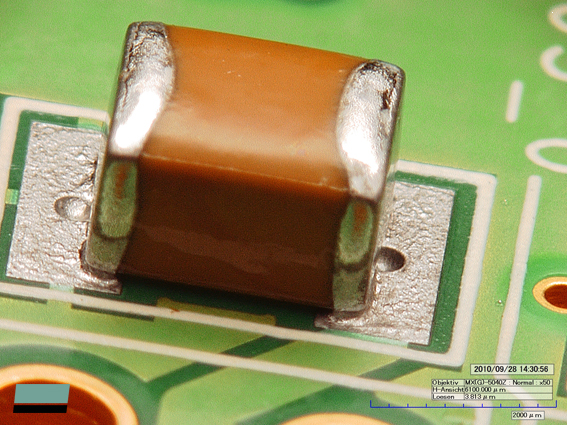

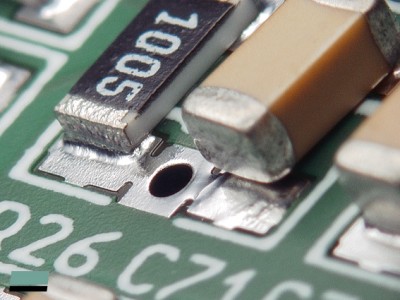

Lotabfluß durch offene Durchkontaktierung mit partiellem Tombstoning

Parallel dazu hat sich die Leiterplattentechnologie erheblich weiterentwickelt und damit sind eine ganze Reihe verschiedener Typen von Durchkontaktierungen entstanden. Neben solchen Vias die komplett von einer auf die andere Seite der Leiterplatte durchgehen, gibt es blind-Vias und Microvias, die einseitig geschlossen sind, sich aber im Durchmesser und in der Eindringtiefe in die Leiterplatte unterscheiden.

Typabhängig können nur bei offenen Durchkontaktierungen unterschiedliche Risiken für die Zuverlässigkeit der Lötstellen entstehen:

- Abfließen des Lotes über offene Durchkontaktierungen

- Kurzschlüsse auf der gegenüberliegenden Seite

- Offene Lötstellen

- Reduzierung der Entwärmungskapazität von thermischen Anschlußflächen

- Behinderung von Pastendruckprozessen durch Lotanhäufungen auf der gegenüberliegenden Seite

- Lufteinschlüsse

- Starke Porenbildung (Voids) in Lötstellen

Aufgrund dieser vielfältigen Risiken sollten daher Durchkontaktierungen in SMD-Anschlußflächen grundsätzlich gefüllt und mit einer lötbaren Endmetalliserung versehen sein.

Der IPC hat schon vor längerer Zeit den in der Industrie leider noch relativ unbekannten Standard IPC-4761 Design Guide for Protection of Printed Board Via Structures veröffentlicht, in dem die Vor- und Nachteile verschiedener Verfahren zum Verschließen von Vias ausführlich analysiert werden.

Weitere Informationen dazu auf der FED-Internetseite unter folgendem Link IPC-4761